Community Tip - Your Friends List is a way to easily have access to the community members that you interact with the most! X

- Community

- Creo+ and Creo Parametric

- 3D Part & Assembly Design

- Residual information cannot be updated when import...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Residual information cannot be updated when importing logic data in Creo cabling

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Notify Moderator

Residual information cannot be updated when importing logic data in Creo cabling

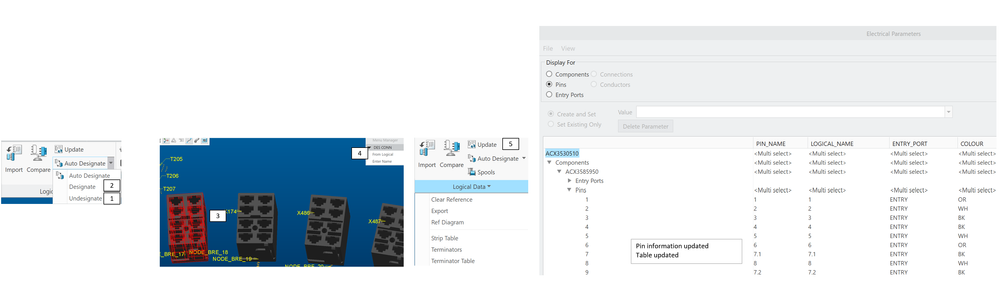

In Creo cabling, if we want to update netlist information, the right process is to "Clear reference" -> "Import Logic data" and then "Update". This process works only in the component(or connector) level, but in the pin level, the residual information is remained and cannot be updated or refreshed completely.

Since we use customized pin information to present the connection table in flat drawing(such as "&mbr.connprm.pin.signal.xxxx"), that means this residual issue will present out-of-date or wrong information in the table when updating a flat drawing.

However, our solution is to proceed "Undesignate" -> "Designate" -> "Update" for a connector, so that all pin information in this connector can be refreshed and completely align with the latest logic data. But that means designer need to do this for every signal connector manually one by one whenever the schematic is revised, which is a big issue for our drawing process.

Is there any ideas or better solution to solve this? For my opinion, the command "Update" should be capable to make all information of current connector completely align with the latest logic data, not partially updated added.

- Labels:

-

3D Animation

-

Assembly Design

-

Data Exchange